案例&资讯

SRAM存储单元读操作分析

来源:宇芯有限公司 日期:2020-04-28 10:10:41

一个典型的SRAM基本结构中,每个存储单元都通过字线和位线与它所在的行和列中的其它存储单元有电学连接关系。水平方向的连线把所有的存储单元连成一行构成字线,而垂直方向的连线是数据输入和数据输出存储单元的通路,称为位线。每一个存储单元都能通过选择适当的字线和位线被唯一地定位。宇芯有限公司介绍关于SRAM存储器的读操作分析。

SRAM存储单元读操作分析

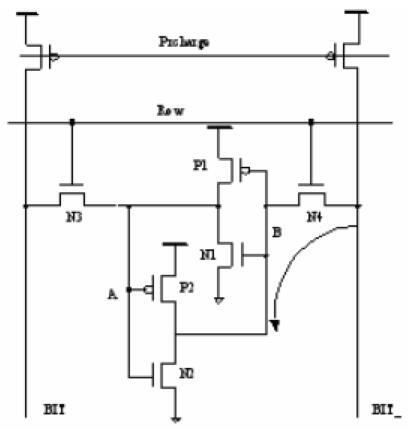

存储单元的读操作是指被寻址的存储单元将它存储的数据送到相应位线上的操作。图3.5 表示的是进行读操作的一个SRAM单元,两条位线开始都是浮空为高电平。假设当前单元中存储的值为逻辑“1”,即节点A为高电平,节点B为低电平。

读操作开始前,位线BIT和BIT_被预充电,预充电平的典型值是电源电压。读操作过程中字线ROW被驱动到高电平,打开传输管N3 和N4。由于节点A为高电平,节点B为低电平,位线BIT_就会经过N4 和N2 放电,电平逐渐降低;此时,由于N3管源漏电压近似相等,因此只有很小的电流流过,位线BIT会继续保持高电平状态。

随着BIT_的放电,BIT和BIT_之间的差分电压逐渐增大;差分电压增大到一定程度后,灵敏放大器将放大并输出差分电压。但操作有两点需要我们注意:当字线电平升高之后,N4 和N2 的分压作用将使节点B的电平升高,很可能使得N1 导通,从而对节电A放电。如果泄放掉的电荷较少(VGS≥Vth,若泄放电的电荷较多,有可能使得N3 管截止),可能导致N3 打开,位线BIT会放电,增加差分电压的建立时间;如果泄放电的电荷较多,那么P2 就可能成为导通状态,进一步抬高B点的电平,从而使得存储数据从“1”翻转为“0”,即发生所谓的“读翻转”。

VTI代理宇芯有限公司SRAM存储器型号

关键词:SRAM SRAM读写

宇芯有限公司自成立以来,我们专注于代理国内外各大知名品牌的半导体元器件,代理品牌有NETSOL、JSC、everspin代理、来杨Lyontek、ISSI、CYPRESS等多个品牌总代理资质,主要产品线为sram、mram、psram等其他存储器芯片,致力于为客户提供具有竞争优势的产品,是一家专业提供存储方案解决商。

图1 六管单元的读出操作

SRAM存储单元读操作分析

存储单元的读操作是指被寻址的存储单元将它存储的数据送到相应位线上的操作。图3.5 表示的是进行读操作的一个SRAM单元,两条位线开始都是浮空为高电平。假设当前单元中存储的值为逻辑“1”,即节点A为高电平,节点B为低电平。

读操作开始前,位线BIT和BIT_被预充电,预充电平的典型值是电源电压。读操作过程中字线ROW被驱动到高电平,打开传输管N3 和N4。由于节点A为高电平,节点B为低电平,位线BIT_就会经过N4 和N2 放电,电平逐渐降低;此时,由于N3管源漏电压近似相等,因此只有很小的电流流过,位线BIT会继续保持高电平状态。

随着BIT_的放电,BIT和BIT_之间的差分电压逐渐增大;差分电压增大到一定程度后,灵敏放大器将放大并输出差分电压。但操作有两点需要我们注意:当字线电平升高之后,N4 和N2 的分压作用将使节点B的电平升高,很可能使得N1 导通,从而对节电A放电。如果泄放掉的电荷较少(VGS≥Vth,若泄放电的电荷较多,有可能使得N3 管截止),可能导致N3 打开,位线BIT会放电,增加差分电压的建立时间;如果泄放电的电荷较多,那么P2 就可能成为导通状态,进一步抬高B点的电平,从而使得存储数据从“1”翻转为“0”,即发生所谓的“读翻转”。

VTI代理宇芯有限公司SRAM存储器型号

| 型号 | 位宽 | 容量 | 温度 | 电压(V) | 速度(ns) | C/S Option | 封装 | 包装 | 状态 |

|---|---|---|---|---|---|---|---|---|---|

| VTI508NL16 | 512K x 16 | 8Mbit | Industrial | 3.3 | 45/55 | 1C/S | 44TSOP2 | Tray | MP |

| VTI508NL16 | 512K x 16 | 8Mbit | Industrial | 3.3 | 45/55 | 1C/S | 48BGA | Tray | MP |

| VTI508HB08 | 1M x 8 | 8Mbit | Industrial | 5.0 | 45/55 | 2C/S | 48BGA | Tray | MP |

| VTI508HB08 | 1M x 8 | 8Mbit | Industrial | 5.0 | 45/55 | 2C/S | 44TSOP2 | Tray | MP |

| VTI508NB16 | 512K x 16 | 8Mbit | Industrial | 3.3 | 45/55 | 2C/S | 48BGA | Tray | MP |

| VTI508NB16 | 512K x 16 | 8Mbit | Industrial | 3.3 | 45/55 | 2C/S | 44TSOP2 | Tray | MP |

| VTI508NB08 | 1M x 8 | 8Mbit | Industrial | 3.3 | 45/55 | 2C/S | 48BGA | Tray | MP |

| VTI508NB08 | 1M x 8 | 8Mbit | Industrial | 3.3 | 45/55 | 2C/S | 44TSOP2 | Tray | MP |

| VTI508HB16 | 512K x 16 | 8Mbit | Industrial | 5.0 | 45/55 | 2C/S | 48BGA | Tray | MP |

| VTI508HL16 | 512K x 16 | 8Mbit | Industrial | 5.0 | 45/55 | 1C/S | 48BGA | Tray | MP |

| VTI508HL16 | 512K x 16 | 8Mbit | Industrial | 5.0 | 45/55 | 1C/S | 44TSOP2 | Tray | MP |

关键词:SRAM SRAM读写

相关文章:新型存储器与传统存储器介质特性对比

宇芯有限公司自成立以来,我们专注于代理国内外各大知名品牌的半导体元器件,代理品牌有NETSOL、JSC、everspin代理、来杨Lyontek、ISSI、CYPRESS等多个品牌总代理资质,主要产品线为sram、mram、psram等其他存储器芯片,致力于为客户提供具有竞争优势的产品,是一家专业提供存储方案解决商。