案例&资讯

SRAM中的功耗来源

来源:宇芯有限公司 日期:2020-05-15 10:42:45

在CMOS电路中,功耗的来源主要有两个方面

(1)静态功耗,即反向漏电流造成的功耗;

(2)动态功耗,由电路作开关转换时进入过渡区由峰值电流引起的暂态功耗,以及负载电容和芯片内寄生电容的充放电电流引起的功耗。

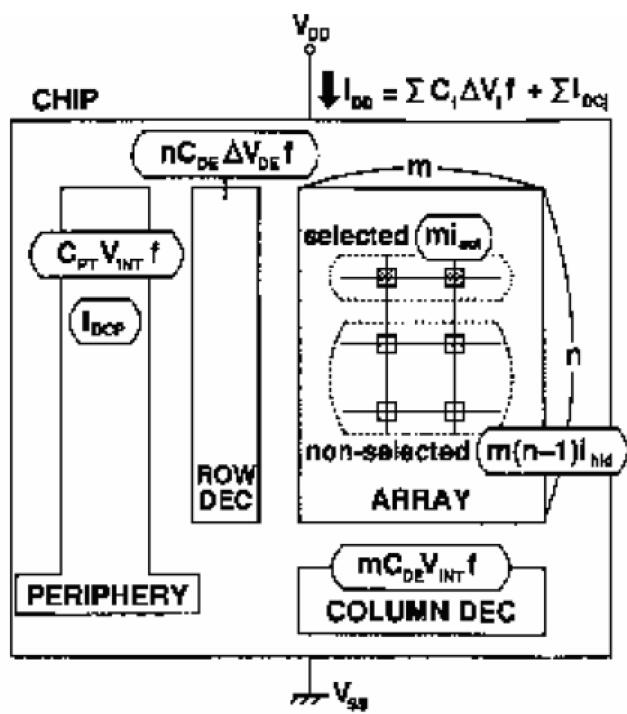

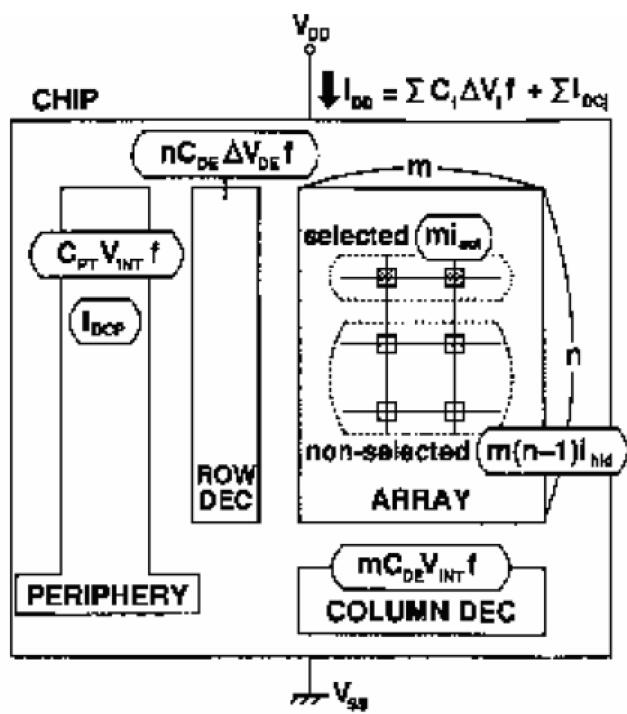

SRAM的功耗包括动态功耗(数据读写时的功耗)和静态功耗(数据保持时的功耗)。图4.1 给出了一个用来分析SRAM功耗来源的结构模型[18],在这个模型中,将SRAM的功耗来源分成三部分:存储阵列、行(列)译码器、以及外围电路。

图1 SRAM中的功耗来源

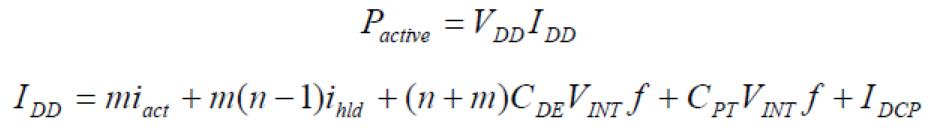

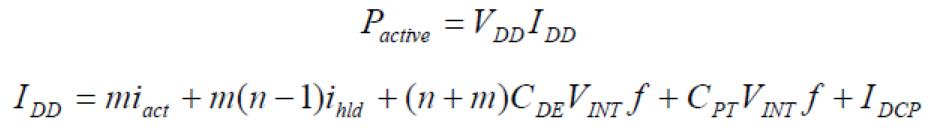

假设存储阵列的规模为n 行m 列,那么当行译码有效后某一行上的m 个存储单元会同时处于活动状态。这样,SRAM 的动态功耗可以表示为:

其中,VDD是外部供电电压,IDD是总电流,iact是选中单元的有效电流,ihld是未选中单元的漏电流,CDE是译码器每个输出节点的电容,VINT是内部工作电压,CPT是CMOS控制逻辑和外围驱动电路的总电容,IDCP是外围电路的静态电流,f是工作频率(f=1/tRC:tRC是操作周期时间),IDCP表示外围电路的总电流,它主要来源于列操作电路和I/O灵敏放大电路。在Vth不太小时,SRAM中的静态漏电流ihld很小,但是,随着器件尺寸和工作电压的降低,漏电流成变得非常严重。对于现在的SRAM设计,其行译码器通常采用CMOS NAND结构[21] ( )C V f DE INT ,因此充电电流n + m 可以忽略,因为每次操作只是选中阵列中的一行和一列(即n + m = 2 )。

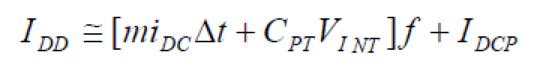

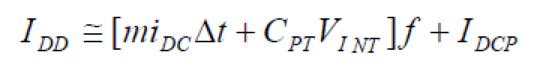

假设字线的活动时间为,位线上的电流为,由于读出操作时位线上的电压变化很小(一般只有0.1~0.3V),所以位线上的充电电流可以忽略不计,但必须注意的是,写入操作时位线上的电流是不能够忽略的,这样,读操作时的电流可以表示为:

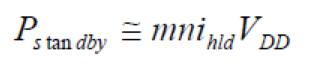

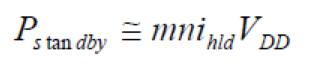

SRAM中的静态功耗主要来自于存储单元的漏电流,与相比, 可以忽略,因此,其静态功耗可以表示为:

关键词:SRAM

宇芯有限公司自成立以来,我们专注于代理国内外各大知名品牌的半导体元器件,代理品牌有NETSOL、JSC、everspin代理、来杨Lyontek、ISSI、CYPRESS,VTI等多个品牌总代理资质,主要产品线为sram、mram、psram等其他存储器芯片,致力于为客户提供具有竞争优势的产品,是一家专业提供存储方案解决商。

(1)静态功耗,即反向漏电流造成的功耗;

(2)动态功耗,由电路作开关转换时进入过渡区由峰值电流引起的暂态功耗,以及负载电容和芯片内寄生电容的充放电电流引起的功耗。

SRAM的功耗包括动态功耗(数据读写时的功耗)和静态功耗(数据保持时的功耗)。图4.1 给出了一个用来分析SRAM功耗来源的结构模型[18],在这个模型中,将SRAM的功耗来源分成三部分:存储阵列、行(列)译码器、以及外围电路。

图1 SRAM中的功耗来源

假设存储阵列的规模为n 行m 列,那么当行译码有效后某一行上的m 个存储单元会同时处于活动状态。这样,SRAM 的动态功耗可以表示为:

其中,VDD是外部供电电压,IDD是总电流,iact是选中单元的有效电流,ihld是未选中单元的漏电流,CDE是译码器每个输出节点的电容,VINT是内部工作电压,CPT是CMOS控制逻辑和外围驱动电路的总电容,IDCP是外围电路的静态电流,f是工作频率(f=1/tRC:tRC是操作周期时间),IDCP表示外围电路的总电流,它主要来源于列操作电路和I/O灵敏放大电路。在Vth不太小时,SRAM中的静态漏电流ihld很小,但是,随着器件尺寸和工作电压的降低,漏电流成变得非常严重。对于现在的SRAM设计,其行译码器通常采用CMOS NAND结构[21] ( )C V f DE INT ,因此充电电流n + m 可以忽略,因为每次操作只是选中阵列中的一行和一列(即n + m = 2 )。

假设字线的活动时间为,位线上的电流为,由于读出操作时位线上的电压变化很小(一般只有0.1~0.3V),所以位线上的充电电流可以忽略不计,但必须注意的是,写入操作时位线上的电流是不能够忽略的,这样,读操作时的电流可以表示为:

SRAM中的静态功耗主要来自于存储单元的漏电流,与相比, 可以忽略,因此,其静态功耗可以表示为:

关键词:SRAM

相关文章:SRAM中灵敏放大器的原理

宇芯有限公司自成立以来,我们专注于代理国内外各大知名品牌的半导体元器件,代理品牌有NETSOL、JSC、everspin代理、来杨Lyontek、ISSI、CYPRESS,VTI等多个品牌总代理资质,主要产品线为sram、mram、psram等其他存储器芯片,致力于为客户提供具有竞争优势的产品,是一家专业提供存储方案解决商。